# AMDA

# Am79C983A

# Integrated Multiport Repeater 2 (IMR2™)

#### DISTINCTIVE CHARACTERISTICS

- Repeater functionality compliant with IEEE 802.3 Repeater Unit specifications

- Hardware implementation of Management Information Base (MIB) with all of the counters, attributes, actions, and notifications specified by IEEE 802.3 Section 19 (Layer Management)

- Twelve pseudo AUI (PAUI™) ports to support multiple media types via direct connection to external transceivers

- One IEEE-compliant AUI port

- One reversible AUI (RAUI™) port that can be programmed as a second AUI port or used to connect directly to a media access controller (MAC)

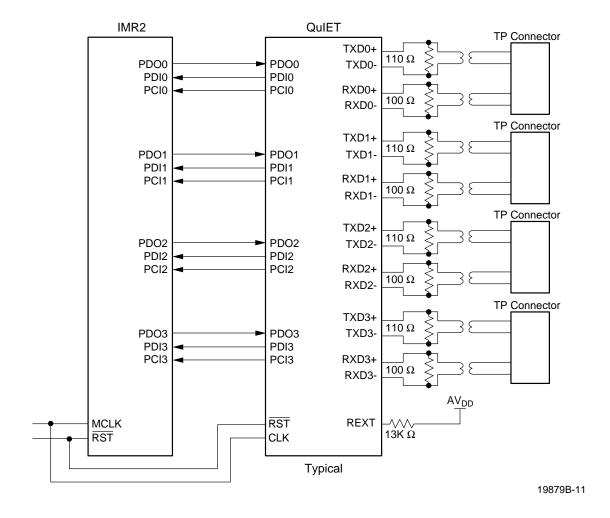

- Direct interface with the AMD Am79C988A QuIET<sup>TM</sup> (Quad Integrated Ethernet Transceiver) to support 10BASE-T repeater designs

- Port switching support to allow individual ports to be switched between multiple Ethernet backplanes under software control

- Remote Monitoring (RMON) Register Bank to provide direct support for etherStatsEntry and etherStatsHistory object groups of the RMON MIB (IETF RFC1757)

- Packet Report Port to provide packet information for deriving objects in the Host, HostTopN, and Matrix groups of the RMON MIB (IETF RFC1578)

- Two user-selectable expansion bus modes: IMR/IMR+ compatible mode and asynchronous mode

- Simple 8-bit microprocessor interface

- Full LED support

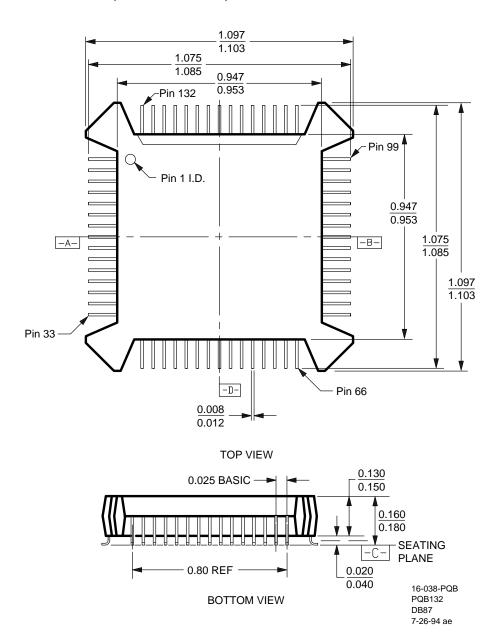

- 132-pin PQFP CMOS device with a single 5-V supply

### **GENERAL DESCRIPTION**

The Am79C983A Integrated Multiport Repeater 2 (IMR2) chip is a VLSI integrated circuit that provides a system-level solution to designing intelligent (managed) multiport repeaters. When the IMR2 device is combined with the Quad Integrated Ethernet Transceiver (QuIET) device, it provides a cost-effective solution to designing 10BASE-T managed repeaters. The IMR2 device integrates the repeater functions specified by Section 9 (Repeater Unit) and Section19 (Layer Management for 10 Mb/s Baseband Repeaters) of the IEEE 802.3 standard.

The Am79C983A IMR2 device provides 1 standard Attachment Unit Interface (AUI) port, 12 Pseudo Attachment Unit Interface (PAUI) ports, and 1 Reversible AUI (RAUI) port for direct connection to a media access controller (MAC). The pseudo AUI ports can be connected to external transceivers to support multiple media types, including 10BASE2, 10BASE-T, and 10BASE-FL/FOIRL. The pseudo AUI ports can be turned off individually (without external circuitry) to allow the switching of transceiver

ports between IMR2 devices. This capability allows multiple IMR2 devices to be connected to a single set of transceivers, thus allowing straightforward implementations of port switching applications.

The IMR2 device also provides a Hardware Implemented Management Information Base (HIMIB™), which is a super set of the functions provided by the Am79C987 HIMIB device. All of the necessary counters, attributes, actions, and notifications specified by Section 19 of the IEEE 802.3 standard are included in the IMR2 device. To facilitate the design of managed repeaters, the IMR2 device implements a simple 8-bit microprocessor interface.

Support for an RMON MIB, as specified by the Internet Engineering Task Force (IETF) RFC 1757, is provided. Direct support is from an RMON Register Bank. Additional support is provided by the Packet Report Port, which supplies information that can be used in conjunction with a microprocessor to derive various RMON MIB attributes. With systems using multiple IMR2 de-

vices, the information is passed to a designated IMR2 device that transfers the information to a MAC.

For application examples on building fully-managed repeaters using the IMR2 and QuIET devices, refer to AMD's *IMR2 Technical Manual* (PID 19898A).

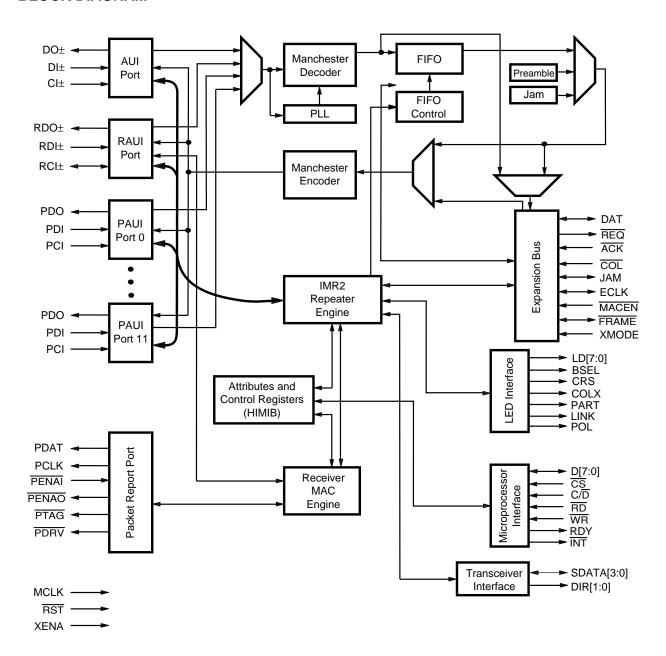

# **BLOCK DIAGRAM**

19879B-1

# **RELATED AMD PRODUCTS**

| Part No.  | Description                                                                                 |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------|--|--|--|--|

| Am79C981  | Integrated Multiport Repeater+ (IMR+™)                                                      |  |  |  |  |

| Am79C982  | basic Integrated Multiport Repeater (bIMR™)                                                 |  |  |  |  |

| Am79C987  | Hardware Implemented Management Information Base (HIMIB™)                                   |  |  |  |  |

| Am79C988A | Quad Integrated Ethernet Transceiver (QuIET™)                                               |  |  |  |  |

| Am7990    | Local Area Network Controller for Ethernet (LANCE)                                          |  |  |  |  |

| Am7996    | IEEE 802.3/Ethernet/Cheapernet Transceiver                                                  |  |  |  |  |

| Am79C90   | CMOS Local Area Network Controller for Ethernet (C-LANCE)                                   |  |  |  |  |

| Am79C98   | Twisted Pair Ethernet Transceiver (TPEX)                                                    |  |  |  |  |

| Am79C100  | Twisted Pair Ethernet Transceiver Plus (TPEX+)                                              |  |  |  |  |

| Am79C900  | Integrated Local Area Communications Controller (ILACC™)                                    |  |  |  |  |

| Am79C940  | Media Access Controller for Ethernet (MACE™)                                                |  |  |  |  |

| Am79C960  | PCnet™-ISA Single-Chip Ethernet Controller (for ISA bus)                                    |  |  |  |  |

| Am79C961  | PCnet™-ISA+ Single-Chip Ethernet Controller for ISA (with Microsoft® Plug n' Play® Support) |  |  |  |  |

| Am79C961A | PCnet™-ISA II Full Duplex Single-Chip Ethernet Controller for ISA                           |  |  |  |  |

| Am79C965  | PCnet™-32 Single-Chip 32-Bit Ethernet Controller                                            |  |  |  |  |

| Am79C970  | PCnet™-PCI Single-Chip Ethernet Controller (for PCI bus)                                    |  |  |  |  |

| Am79C970A | PCnet™-PCI II Full Duplex Single-Chip Ethernet Controller (for PCI bus)                     |  |  |  |  |

| Am79C974  | PCnet™-SCSI Combination Ethernet and SCSI Controller for PCI Systems                        |  |  |  |  |

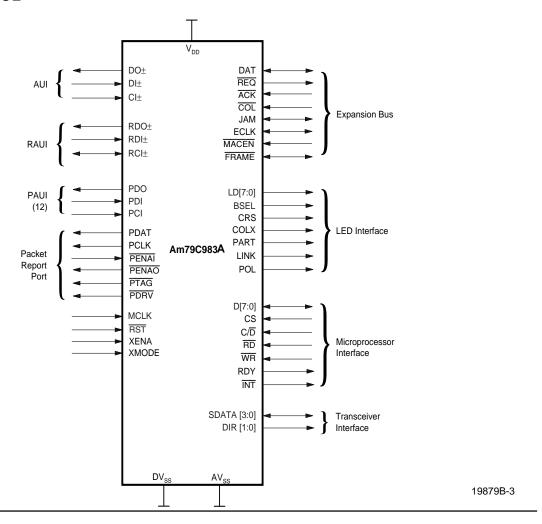

#### **CONNECTION DIAGRAM**

#### **PQFP** PCI[11] PDI[11] PCI[10] PDI[10] PCI[9] PDI[9] PCI[7] PDI[7] PCI[6] PCI[6] PDI[8] AVss PCI[5] PDI[5] V<sub>DD</sub> PCI[4] PDI[4] PCI[8] PD[[3] PCI[2] PDI[2] PCI[1] PDI[1] PCI[0] V<sub>DD</sub> RDI+ 118 117 116 115 114 110 109 108 107 105 105 103 100 100 7 DO-[ 99 RDO-2 98 RDO+ DO+ 3 97 □ RCI-DI-□ RCI+ 4 96 DI+ 5 ■ DV<sub>SS</sub> CI-E 95 6 □ DIR[1] CI+ C 94 ☐ DIR[0] 7 93 DV<sub>SS</sub> $\Box$ ☐ SDATA[3] 8 MACEN 92 ■ DV<sub>SS</sub> COL 9 91 **ACK** 10 90 ☐ SDATA[2] 11 89 ☐ SDATA[1] XMODE [ REQ 12 88 ☐ SDATA[0] DAT 13 87 $\Box$ $V_{DD}$ ☐ XENA JAM [ 14 86 85 RST 15 $V_{DD}$ ■ DV<sub>SS</sub> 84 ECLK [ 16 17 83 ☐ MCLK FRAME Am79C983A ■ DV<sub>SS</sub> DV<sub>SS</sub> **L** 18 82 81 BSEL **PDRV** 19 □ CRS 20 80 PDAT **C** 21 79 □ COLX PTAG L ☐ PART PCLK [ 22 78 23 77 LINK DV<sub>SS</sub> $\Box$ $\Box$ $V_{DD}$ PENAO L 24 76 25 75 ☐ POL PENAI 26 74 ☐ LD[7] DV<sub>SS</sub> $\Box$ **MATCHI** L 27 73 ☐ LD[6] 72 DVss MATCHO 28 29 71 ■ LD[5] PSL 70 V<sub>DD</sub> **C** 30 ☐ LD[4] INT 31 69 ■ DV<sub>SS</sub> RDY [ 32 68 ☐ LD[3] 33 67 \_ LD[2] DV<sub>SS</sub> [ DV<sub>SS</sub> [ DATA[3] [ DATA[2] [ DATA[1] [ DATA[0] [ PDO[11] [ PDO[10] [ PDO[9] [ PDO[8] [ DVss [ PDO[7] [ PDO[7] [ V<sub>DD</sub> [ PDO[5] [ PDO[4] [ DV<sub>SS</sub> [ PDO[3] [ PDO[2] [ V<sub>DD</sub> [ PDO[1] [ PDO[0] [ V<sub>DD</sub>

19879B-2

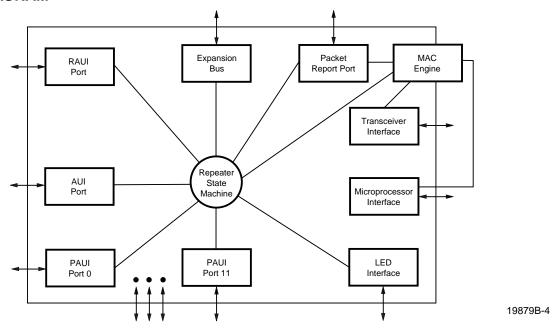

# **LOGIC SYMBOL**

# **LOGIC DIAGRAM**

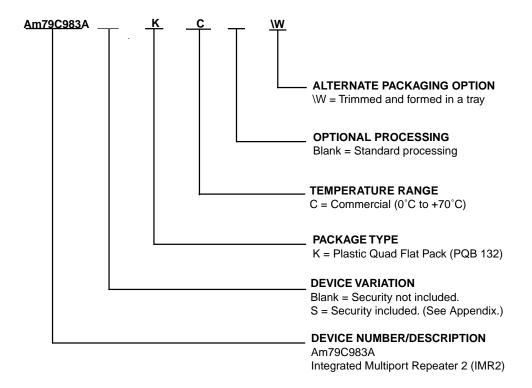

# ORDERING INFORMATION

# **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Co  | mbinations |

|-----------|------------|

| Am79C983A | KC, KC\W   |

# **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

# **TABLE OF CONTENTS**

| DISTINCTIVE CHARACTERISTICS                              | 1  |

|----------------------------------------------------------|----|

| GENERAL DESCRIPTION                                      | 1  |

| BLOCK DIAGRAM                                            | 3  |

| RELATED AMD PRODUCTS                                     |    |

| CONNECTION DIAGRAM                                       |    |

| LOGIC SYMBOL                                             |    |

| LOGIC DIAGRAM                                            |    |

| ORDERING INFORMATION                                     |    |

|                                                          |    |

| Standard Products                                        |    |

| PIN DESIGNATIONS                                         |    |

| PIN DESCRIPTION                                          |    |

| Pseudo AUI Pins                                          |    |

| RAUI Port Pins                                           |    |

| AUI Pins                                                 |    |

| Expansion Bus Pins Packet Report Port                    |    |

| Microprocessor Interface                                 |    |

| LED Interface                                            |    |

| Miscellaneous Pins                                       |    |

| Transceiver Device Interface                             | 15 |

| FUNCTIONAL DESCRIPTION                                   | 17 |

| Overview                                                 | 17 |

| Basic Repeater Functions                                 |    |

| Repeater Function                                        |    |

| Signal Regeneration                                      |    |

| Jabber Lockup Protection                                 |    |

| Collision Handling                                       |    |

| Fragment Extension                                       |    |

| Basic Management Functions                               |    |

| Repeater Management                                      |    |

| RMON                                                     |    |

| Packet Reports                                           | 18 |

| Detailed Functions                                       |    |

| Reset                                                    |    |

| Hardware Reset                                           |    |

| Software Reset                                           |    |

| Expansion Bus  Synchronous Mode Operation                |    |

| Asynchronous Mode Operation                              |    |

| Packet Statistics                                        |    |

| Packet Report Port                                       |    |

| RAUI Port                                                | 25 |

| Error Packet Statistics                                  |    |

| Transceiver Interface                                    |    |

| PAUI Ports                                               |    |

| QuIET Device Control and Status Data Interface           |    |

| QuIET Device Control and Status Data Interface Operation |    |

| Visual Status Monitoring (LED) Support                   |    |

| Using AUI/RAUI for 10BASE-T Ports                        |    |

| Intrusion Protection                                     |    |

| Timer Values                                             | 29 |

# PRELIMINARY

| Microprocessor Interface                             |    |

|------------------------------------------------------|----|

| Management Functions                                 | 29 |

| Status Register                                      | 30 |

| Register Bank 0: Repeater Registers                  |    |

| Source Address Match Register                        | 30 |

| Total Octets                                         | 31 |

| Transmit Collisions                                  | 31 |

| Configuration Register                               | 31 |

| Repeater Status                                      |    |

| QuIET Device Transceiver ID Register                 | 31 |

| Repeater Device and Revision Register                | 32 |

| Device Configuration                                 | 32 |

| Register Bank 1: Interrupts                          | 32 |

| Port Partition Status Change Interrupt               | 32 |

| Runts with Good FCS Interrupt                        | 32 |

| Link Status Change Interrupt                         | 32 |

| Loopback Error Change Interrupt                      | 33 |

| Polarity Change Interrupt                            | 33 |

| SQE Test Error Change Interrupt                      | 33 |

| Source Address Changed Interrupt                     | 33 |

| Intruder Interrupt                                   | 33 |

| Source Address Match Interrupt                       | 33 |

| Data Rate Mismatch Interrupt                         | 34 |

| Transceiver Interface Status                         | 34 |

| Transceiver Interface Change Interrupt               | 34 |

| Jabber Interrupt                                     |    |

| Register Bank 2: Interrupt Control Registers         |    |

| Partition Status Change Interrupt Enable             |    |

| Runts with Good FCS Interrupt Enable                 |    |

| Link Status Change Interrupt Enable                  |    |

| Loopback Error Change Interrupt Enable               |    |

| Polarity Change Interrupt Enable                     |    |

| SQE Test Error Change Interrupt Enable               |    |

| Source Address Changed Interrupt Enable              |    |

| Intruder Interrupt Enable                            |    |

| Multicast Address Pass Enable                        |    |

| Data Rate Mismatch Interrupt Enable                  |    |

| Last Source Address Compare Enable                   |    |

| Preferred Address Compare Enable                     |    |

| Transceiver Interface Changed Interrupt Enable       | 36 |

| Jabber Interrupt Enable                              | 36 |

| Register Bank 3: Port Control Registers              |    |

| Alternative Reconnection Algorithm Enable            |    |

| Link Test Enable                                     |    |

| Link Pulse Transmit Enable                           |    |

| Automatic Receiver Polarity Reversal Enable          |    |

| SQE Mask Enable                                      |    |

| Port Enable/Disable                                  |    |

| Port Switching Control                               | 37 |

| Extended Distance Enable                             |    |

| Automatic Last Source Address Intrusion Control      | 38 |

| Automatic Preferred Source Address Intrusion Control |    |

| Last Source Address Lock Control                     |    |

| Register Bank 4: Port Status Registers               |    |

| Partitioning Status of Ports                         |    |

| Link Test Status of Ports                            |    |

| Loopback Error Status                                | 39 |

| Receive Polarity Status                              |    |

| SQE Test Status                                                            |      |

|----------------------------------------------------------------------------|------|

| Register Bank 5: RMON Registers                                            | 39   |

| etherStatsOctets                                                           |      |

| etherStatsPkts                                                             |      |

| etherStatsBroadcastPkts                                                    |      |

| etherStatsMulticastPkts                                                    |      |

| etherStatsCRCAlignErrors                                                   |      |

| etherStatsUndersizePkts                                                    |      |

| etherStatsOversizePkts                                                     |      |

| etherStatsFragments                                                        |      |

| etherStatsJabbers                                                          |      |

| etherStatsCollisions                                                       |      |

| etherStats64Octets                                                         |      |

| etherStats65to127Octets                                                    |      |

| etherStats128to255Octets                                                   |      |

| etherStats256to511Octets                                                   |      |

| etherStats512to1023Octets                                                  |      |

| etherStats1024to1518Octets                                                 |      |

| Activity                                                                   |      |

| Register Bank 7: Management Support                                        |      |

| Device ID                                                                  |      |

| Sample Error Status                                                        |      |

| Report Packet Size                                                         |      |

| STATS Control                                                              |      |

| Register Banks 16 through 30: Port Attribute Registers                     |      |

| Readable Octets                                                            |      |

| Frame Check Sequence (FCS) Errors                                          |      |

| Alignment Errors                                                           |      |

| Frames Too Long                                                            |      |

| Short Events                                                               |      |

| Runts                                                                      |      |

| Collisions                                                                 |      |

| Late Events                                                                |      |

| Very Long Events                                                           |      |

| Data Rate Mismatches                                                       |      |

| Auto Partitions                                                            | 44   |

| Source Address Changes                                                     | 44   |

| Readable Broadcast Frames                                                  | 44   |

| Last Source Address                                                        | 44   |

| Readable Multicast Frames                                                  |      |

| Preferred Source Address                                                   | 44   |

| SYSTEM APPLICATIONS                                                        | . 45 |

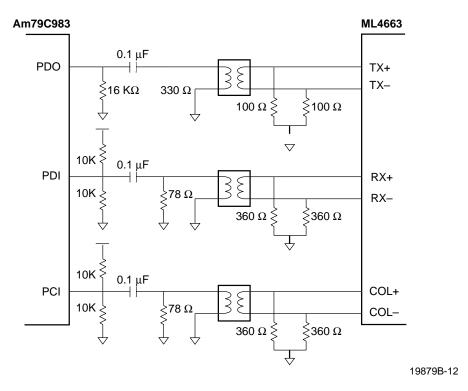

| IMR2 to QuIET Connection                                                   | 45   |

| Other Media                                                                |      |

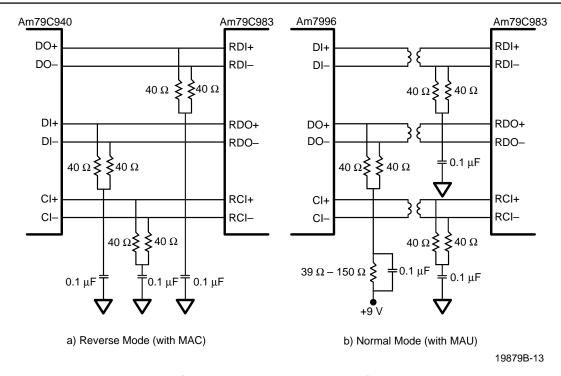

| MAC Interface                                                              |      |

| RAUI Port                                                                  |      |

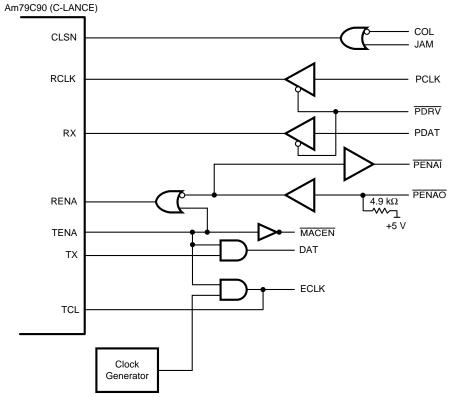

| PR Port Configuration                                                      |      |

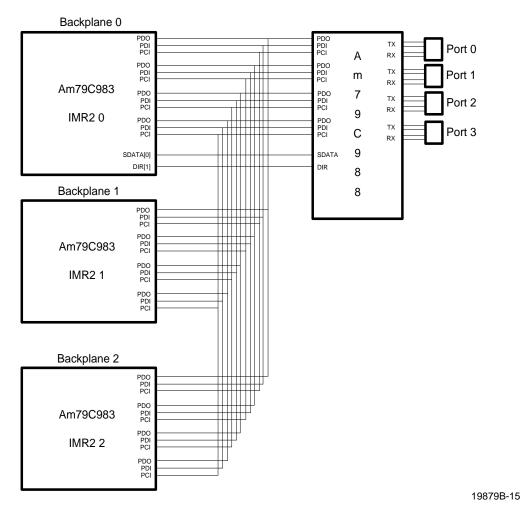

| Port Switching                                                             |      |

| ABSOLUTE MAXIMUM RATINGS                                                   |      |

| OPERATING RANGES                                                           |      |

| DC CHARACTERISTICS over operating ranges unless otherwise specified        |      |

| SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified |      |

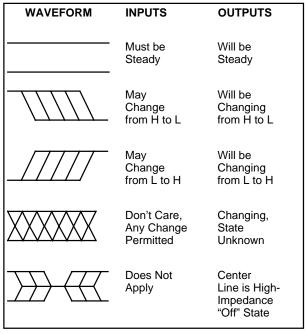

| KEY TO SWITCHING WAVEFORMS                                                 |      |

|                                                                            |      |

| SWITCHING WAVEFORMS                                                        |      |

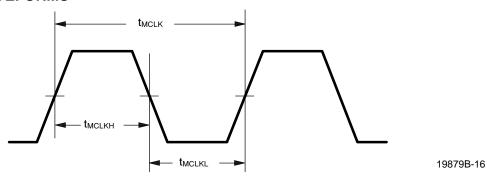

| Master Clock (MCLK) Timing                                                 | 54   |

# PRELIMINARY

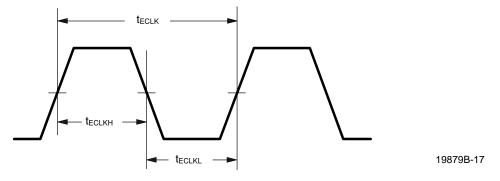

| Expansion Bus Asynchronous Clock (ECLK) Timing     | 54 |

|----------------------------------------------------|----|

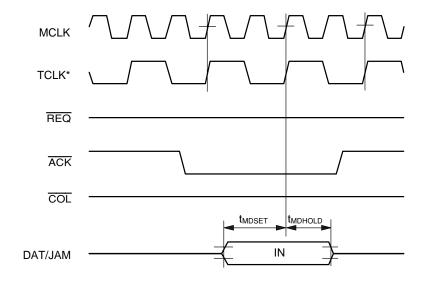

| Expansion Bus Input Timing - Synchronous Mode      |    |

| Expansion Bus Output Timing - Synchronous Mode     |    |

| Expansion Port Collision Timing - Synchronous Mode | 56 |

| Packet Report Port Timing                          | 56 |

| Expansion Port Input Timing - Asynchronous Mode    | 56 |

| Expansion Port Output Timing - Asynchronous Mode   | 57 |

| PAUI PDO Transmit                                  |    |

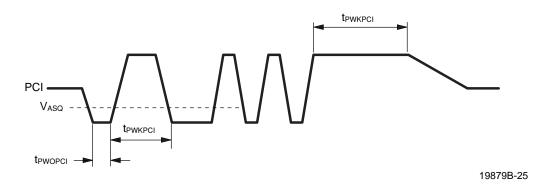

| PAUI PCI Receive                                   | 57 |

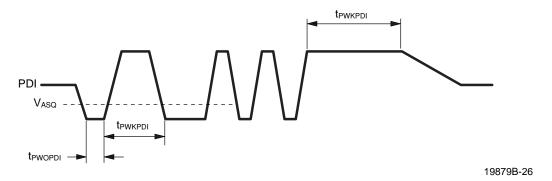

| PAUI Receive                                       | 58 |

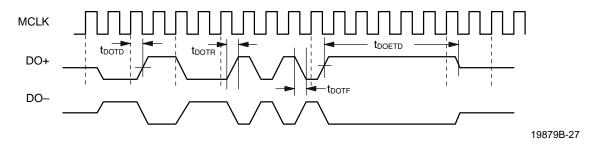

| (R)AUI Timing                                      | 58 |

| (R)AUI Receive                                     | 58 |

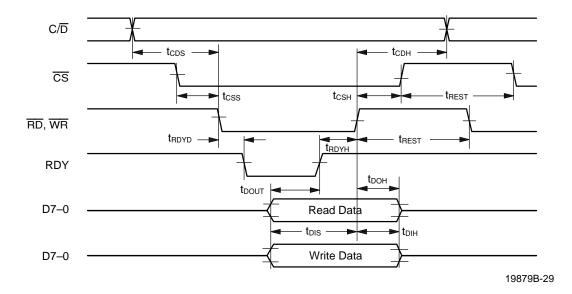

| Microprocessor Bus Interface Timing                | 59 |

| HYSICAL DIMENSIONS                                 | 60 |

# PIN DESIGNATIONS Listed by Pin Number

| Pin No. | Pin Name |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | DO-      | 34      | WR       | 67      | LD[2]    | 100     | AVss     |

| 2       | DO+      | 35      | RD       | 68      | LD[3]    | 101     | RDI+     |

| 3       | DI-      | 36      | CS       | 69      | DVss     | 102     | RDI-     |

| 4       | DI+      | 37      | C/D      | 70      | LD[4]    | 103     | VDD      |

| 5       | CI-      | 38      | D[7]     | 71      | LD[5]    | 104     | PDI[0]   |

| 6       | CI+      | 39      | D[6]     | 72      | DVss     | 105     | PCI[0]   |

| 7       | DVss     | 40      | D[5]     | 73      | LD[6]    | 106     | PDI[1]   |

| 8       | MACEN    | 41      | D[4]     | 74      | LD[7]    | 107     | PCI[1]   |

| 9       | COL      | 42      | DVss     | 75      | POL      | 108     | PDI[2]   |

| 10      | ACK      | 43      | D[3]     | 76      | VDD      | 109     | PCI[2]   |

| 11      | XMODE    | 44      | D[2]     | 77      | LINK     | 110     | PDI[3]   |

| 12      | REQ      | 45      | D[1]     | 78      | PART     | 111     | PCI[3]   |

| 13      | DAT      | 46      | D[0]     | 79      | COLX     | 112     | PDI[4]   |

| 14      | JAM      | 47      | VDD      | 80      | CRS      | 113     | PCI[4]   |

| 15      | VDD      | 48      | PDO[11]  | 81      | BSEL     | 114     | Vdd      |

| 16      | ECLK     | 49      | PDO[10]  | 82      | DVss     | 115     | PDI[5]   |

| 17      | FRAME    | 50      | PDO[9]   | 83      | MCLK     | 116     | PCI[5]   |

| 18      | DVss     | 51      | PDO[8]   | 84      | DVss     | 117     | AVss     |

| 19      | PDRV     | 52      | DVss     | 85      | RST      | 118     | PDI[6]   |

| 20      | PDAT     | 53      | PDO[7]   | 86      | XENA     | 119     | PCI[6]   |

| 21      | PTAG     | 54      | PDO[6]   | 87      | VDD      | 120     | PDI[7]   |

| 22      | PCLK     | 55      | VDD      | 88      | SDATA[0] | 121     | PCI[7]   |

| 23      | DVss     | 56      | PDO[5]   | 89      | SDATA[1] | 122     | PDI[8]   |

| 24      | PENAO    | 57      | PDO[4]   | 90      | SDATA[2] | 123     | PCI[8]   |

| 25      | PENAI    | 58      | DVss     | 91      | DVss     | 124     | AVss     |

| 26      | DVss     | 59      | PDO[3]   | 92      | SDATA[3] | 125     | PDI[9]   |

| 27      | MATCHI   | 60      | PDO[2]   | 93      | DIR[0]   | 126     | PCI[9]   |

| 28      | MATCHO   | 61      | VDD      | 94      | DIR[1]   | 127     | AVss     |

| 29      | PS       | 62      | PDO[1]   | 95      | DVss     | 128     | PDI[10]  |

| 30      | VDD      | 63      | PDO[0]   | 96      | RCI+     | 129     | PCI[10]  |

| 31      | ĪNT      | 64      | LD[0]    | 97      | RCI-     | 130     | PDI[11]  |

| 32      | RDY      | 65      | LD[1]    | 98      | RDO+     | 131     | PCI[11]  |

| 33      | DVss     | 66      | NC       | 99      | RDO-     | 132     | VDD      |

# PIN DESCRIPTION

# **Pseudo AUI Pins**

PDO<sub>0-11</sub> Pseudo AUI Data Output Output/High Impedance

PDO is a single-ended output driver. PDO can be placed into a high impedance state, allowing multiple IMR2 devices to connect to a single QuIET device (port switching). The output data is Manchester encoded.

PDI<sub>0-11</sub> Pseudo AUI Receive Data Input Input

The input data is Manchester encoded.

PCI<sub>0-11</sub> Pseudo AUI Collision Input Input

PAUI port collision data receiver. A 10-MHz square wave indicates a collision has been detected on that port.

#### **RAUI Port Pins**

RDO+, RDO-Reversible AUI Data Output Output

RDO is a differential, Manchester output driver.

RDI+, RDI-Reversible AUI Data Input Input

RDI is a differential, Manchester receiver.

RCI+, RCI-Reversible AUI Collision Input Input/Output

RCI is a differential I/O. As an input, RCI receives a collision indication. As an output, RCI generates a 10-MHz square wave when a collision is sensed.

PS Output

This pin is reserved for factory use.

**AUI Pins**

DO+, DO-AUI Data Output Output

AUI port differential driver. Manchester encoded data.

DI+, DI-AUI Data Input Input

AUI port differential receiver. Manchester encoded data.

CI+, CI-AUI Collision Input

Input

AUI port collision differential receiver.

# **Expansion Bus Pins**

DAT Data

#### Input/Output/High Impedance

The IMR2 device drives the DAT line with NRZ data when both  $\overline{REQ}$  and  $\overline{ACK}$  pins are asserted. DAT is an input if only the  $\overline{ACK}$  signal is asserted. If  $\overline{REQ}$  and  $\overline{ACK}$  are not asserted, DAT enters a high impedance state. During collision when JAM is HIGH, DAT is used to signal a multiport (DAT=0) or single port (DAT=1) condition.

JAM

Jam

# Input/Output/High Impedance

This pin is an output if the device is the only active IMR2 device. An IMR2 device is defined as active when it has one or more ports receiving or colliding, is in the state where it is still transmitting data from the internal FIFO, or is extending a packet to the minimum 96-bit times. If active, the IMR2 device drives the JAM pin HIGH to indicate that it is in a Collision state when both  $\overline{\text{REQ}}$  and  $\overline{\text{ACK}}$  pins are asserted. JAM is an input if only the  $\overline{\text{ACK}}$  signal is asserted. If  $\overline{\text{REQ}}$  and  $\overline{\text{ACK}}$  are not asserted, JAM enters a high impedance state.

REQ Request Output, Active LOW

This pin is driven LOW when the IMR2 device senses activity. An IMR2 device is defined as ACTIVE when it has one or more ports receiving or colliding, is in the state where it is still transmitting data from the internal FIFO, or is extending a packet to the minimum 96-bit times. The assertion of this signal signifies that the IMR2 device requires the DAT and JAM lines to transfer repeated data and collision status information to other IMR2 devices.

ACK Acknowledge Input, Active LOW

When this signal is asserted by an external arbiter, it signals to the requesting IMR2 device that it may drive the DAT and JAM pins. It signals to other IMR2 devices the presence of valid collision status on the JAM line and valid data on the DAT line.

# COL Collision Input, Active LOW

When this pin is asserted by an external arbiter, it signifies that more than one IMR2 device is active and that each IMR2 device should generate the Collision Jam Sequence independently.

# ECLK Bus Clock Input/Output

Data transitions on the expansion bus on DAT are synchronized to this clock. ECLK is a 10-MHz output clock when DAT is transmitting and a 10-MHz input clock when DAT is receiving. ECLK is only used when the expansion bus is operated in the asynchronous mode. ECLK should be terminated to ground with a 1 k $\Omega$  resistor. ECLK should be ignored in the synchronous mode.

# MACEN MAC Enable Input, Active LOW

When this pin is asserted, data on the expansion bus is included in MIB statistics. This is typically used when a MAC is driving the expansion bus.

#### **MATCHO**

This pin should be tied to +5 V through a 1 k $\Omega$  ±10% resistor.

#### **MATCHI**

This pin should be tied to +5 V through a 1 k $\Omega$  ±10% resistor.

#### **FRAME**

# Packet Framing Signal Input/Output, Active LOW

FRAME defines the beginning and end of a packet. FRAME indicates valid data on the DAT pin when the expansion bus is in the asynchronous mode. FRAME is an output on the IMR2 device when it is transmitting over the expansion bus. It is an input on all other IMR2 devices.

# XMODE Expansion Bus Mode Input

XMODE determines the mode of the expansion bus. XMODE should not be changed after  $\overline{RST}$ . Although changing XMODE after  $\overline{RST}$  will change the expansion bus mode, the operation is unpredictable. Therefore, it is recommended that XMODE be tied either HIGH or LOW, depending on the desired expansion bus mode.

| XMODE | Mode                   |  |  |  |

|-------|------------------------|--|--|--|

| 1     | Asynchronous           |  |  |  |

| 0     | Synchronous (IMR/IMR+) |  |  |  |

# XENA Port Enable Input

XENA sets the default mode of the ports. It is used when RST transitions from LOW to HIGH.

| XENA | Default                                                                   |  |  |  |

|------|---------------------------------------------------------------------------|--|--|--|

| 1    | All ports are enabled.                                                    |  |  |  |

| 0    | All ports are disabled. The output drivers are in a high impedance state. |  |  |  |

**Note:** XENA only controls the default state. Once reset is completed, the enabling and disabling of ports is under software control. It is recommended that XENA be tied either HIGH or LOW, depending on the desired default state.

# **Packet Report Port**

# PDAT

# Packet Report Output, High Impedance

PDAT outputs the beginning portion of a packet followed by packet status information. The size of the beginning portion is user programmable. If a second packet arrives before PDAT finishes transmitting status information, the second packet and corresponding status information are not transmitted over PDAT. The packet is aborted on collision.

#### **PENAI**

# Packet Report Enable Input Input, Active LOW

PENAI senses when another device is transmitting over PDAT.

#### **PENAO**

# Packet Report Enable Output Output, Active LOW, Open Drain

PENAO is TRUE when the IMR2 device is transmitting data over PDAT. If a second packet arrives before PDAT is finished transmitting status information, PENAO remains active for the second packet.

# PDRV Packet Drive Output, Active LOW

PDRV is TRUE when the IMR2 device is transmitting data over PDAT. If a second packet arrives before PDAT is finished transmitting status, PDRV goes FALSE after the status is transmitted.

# **PCLK**

# Packet Report Clock Output, High Impedance

PCLK is a 10-MHz clock. PDAT transitions are synchronized to PCLK.

#### **PTAG**

**Packet Tag**

# **Output, HIGH Impedance, Active LOW**

PTAG indicates when the status frame is being transmitted over PDAT. It is asserted when the status frame is transmitted.

# **Microprocessor Interface**

D[7:0]

Microprocessor Data

Input/Output

These pins are inputs when either  $\overline{CS}$  or  $\overline{WR}$  are LOW. They are outputs when  $\overline{CS}$  and  $\overline{RD}$  are LOW. Otherwise, these pins are high impedance.

CS

**Chip Select**

Input, Active LOW

This pin enables the IMR2 device to read from or write to the microprocessor data bus.

$C/\overline{D}$

Control/Data

Input

This pin is used to select either a control register or a data register in the IMR2 device and is normally connected to the least significant bit of the address bus.

$\overline{\mathsf{RD}}$

Read Strobe Input. Active LOW

Initiates read operation.

WR

Write Strobe Input, Active LOW

Initiates write operation.

RDY Ready

Output, Active HIGH, Open Drain

RDY is driven LOW at the start of every READ or WRITE cycle. RDY is released when the IMR2 device is ready to complete the transaction.

INT

Interrupt

Output, Active LOW, Open Drain

The Interrupt pin is driven LOW when any of the unmasked (enabled) interrupts occur.

#### **LED Interface**

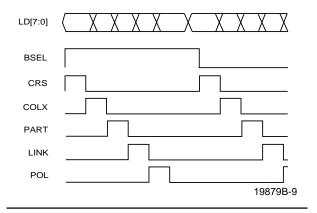

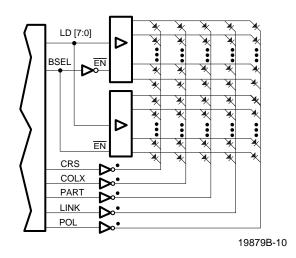

LD[7:0] LED Drivers

LD is the status output and is transmitted as 2 bytes. The byte number (high or low) is determined by BSEL.

**BSEL**

**Byte Select**

#### Output

When BSEL is LOW, LD[7:0] is transmitting the status of the first eight PAUI ports (ports  $P_7$  through  $P_0$ ). When BSEL is HIGH, LD[7:0] is transmitting the status of the rest of the PAUI ports (ports  $P_{11}$  through  $P_8$ ), the AUI port, the RAUI port, and the expansion bus.

#### **CRS**

**Carrier Sense Strobe**

Output

When CRS is HIGH, LD [7:0] has carrier sense status.

COL X

**Collision Status**

Output

When COLX is HIGH, LD [7:0] has collision status.

**PART**

**Partitioning Status**

Output

When PART is HIGH, LD [7:0] has partitioning status.

LINK

**Link Status**

Output

When LINK is HIGH, LD [7:0] has link status.

POL

**Polarity Status**

Output

When POL is HIGH, LD [7:0] has polarity status.

# **Miscellaneous Pins**

RST

Reset

Input

When RST is LOW, the IMR2 device resets to its default state.

**MCLK**

**Master Clock**

Input

MCLK is a 20-MHz clock input.

#### **Transceiver Device Interface**

SDATA [3:0] Serial Data

Input/Output

SDATA carries command and status data between the IMR2 device and the QuIET device (or other connected transceiver).

| Pin       | Transceiver Ports |

|-----------|-------------------|

| SDATA [0] | PAUI [3:0]        |

| SDATA [1] | PAUI [7:4]        |

| SDATA [2] | PAUI [11:8]       |

| SDATA [3] | Arbitrary ports   |

# DIR Direction Output

DIR sets the direction of data on SDATA[3:0] The settings are as follows:

| DIR[1:0] | Function                                     |  |  |  |

|----------|----------------------------------------------|--|--|--|

| 00       | Transceiver (QuIET device) drives SDATA with |  |  |  |

| 00       | status and device ID.                        |  |  |  |

| 01       | SDATA is a high impedance output.            |  |  |  |

| 10       | SDATA is a high impedance output.            |  |  |  |

| 11       | IMR2 device drives SDATA with commands.      |  |  |  |

# V<sub>DD</sub> Power Pin

These pins supply +5 V power.

# AVss Analog Ground Ground Pin

These pins provide the ground reference for the analog portions of the IMR2 circuitry. These pins should be decoupled and kept separate from the digital ground plane.

# DVss Digital Ground Ground Pin

These pins provide the ground reference for the digital portions of the IMR2 circuitry. These pins should be decoupled and kept separate from the analog power plane.

# **FUNCTIONAL DESCRIPTION**

#### Overview

The Am79C983A Integrated Multiport Repeater 2 device provides a system-level solution to designing IEEE 802.3 managed repeaters. It includes 12 pseudo AUI (PAUI) ports for single-ended connections to external transceivers. The IMR2 device interfaces directly with AMD's Am79C988A Quad Integrated Ethernet Transceiver (QuIET) device for 10BASE-T implementations. The PAUI ports can be turned off individually to enable port switching applications. In addition, the IMR2 device has a standard AUI port and a reversible AUI (RAUI) port for a direct connection to a MAC.

The IMR2 device provides a Hardware Implemented Management Information Base (HIMIB) which contains all of the necessary counters, attributes, actions, and notifications specified by Section 19 of the IEEE 802.3 standard. Support for an RMON MIB, as specified by the Internet Engineering Task Force (IETF) RFC 1757, is also provided. Direct support is from an RMON Register Bank. Additional support is provided by the Packet Report Port, which supplies packet information that can be used in conjunction with a microprocessor to derive various RMON MIB attributes.

# **Basic Repeater Functions**

The IMR2 repeater functions are summarized below. An overview of IMR2 management functions is presented under *Basic Management Functions*.

# **Repeater Function**

If any single network port of a repeater system senses the start of a valid packet on its receive lines, the IMR2 device will retransmit the received data to all other enabled network ports unless a collision is detected. The repeated data will also be presented on the DAT line of the expansion bus to facilitate designs utilizing multiple IMR2 devices. The IMR2 device fully complies with Section 9.5.1 of the IEEE 802.3 specifications.

# Signal Regeneration

When retransmitting a packet, the IMR2 device ensures that the outgoing packet complies with the IEEE 802.3 specification in terms of preamble structure. Data packets repeated by the IMR2 device will contain a minimum of 56 preamble bits before the Start of Frame Delimiter.

The IMR2 device, by virtue of its internal Phase Lock Loop and Manchester Encoder/Decoder, will ensure correct regeneration of the repeated signal at its PAUI and AUI outputs. If the outputs of the IMR2 device are connected to QuIET device transceivers, the 10BASE-T outputs of the QuIET devices will meet the IEEE 802.3 signal symmetry requirements. If other types of transceivers are used, the signal characteristics will depend, in part, on the transceiver.

#### **Jabber Lockup Protection**

The IMR2 chip implements a built-in jabber protection scheme to ensure that the network is not disabled due to transmission of excessively long data packets. This protection scheme will automatically interrupt the transmitter circuits of the IMR2 device for 96-bit times, if the IMR2 device has been transmitting continuously for more than 65,536 bit times. This is referred to as MAU Jabber Lockup Protection (MJLP). The MJLP status for the IMR2 chip can be read from the Repeater Status Register.

#### **Collision Handling**

The IMR2 chip will detect and respond to collision conditions as specified in the IEEE 802.3 specification. A multiple IMR2 device repeater implementation also complies with the specification because of the inter-IMR2 chip status communication provided by the expansion port. Specifically, a repeater based on one or more IMR2 devices will handle correctly the transmit collision and one-port-left collision conditions as specified in Section 9 of the IEEE 802.3 specification.

# **Fragment Extension**

If the total packet length received by the IMR2 device is less than 96 bits, including preamble, the IMR2 chip will extend the repeated packet length to 96 bits by appending a Jam sequence to the original fragment. Note that in a few cases, it is possible for the IMR2 device to generate a sequence 97 bits in length when the expansion bus is operated in the asynchronous mode.

#### Auto Partitioning/Reconnection

Any of the IMR2 ports can be partitioned under excessive duration or frequency of collision conditions. Once a port is partitioned, the IMR2 device will continue to transmit data packets to a partitioned port, but will not respond (as a repeater) to activity on the partitioned port's receiver. The IMR2 chip will monitor the port and reconnect it once certain criteria indicating port "wellness" are met. The criteria for reconnection are specified by the IEEE 802.3 standard. In addition to the standard reconnection algorithm, the IMR2 device implements an alternative reconnection algorithm which provides a more robust partitioning function. Each port is partitioned and/ or reconnected separately and independently of other network ports.

Either one of the following conditions occurring on any enabled IMR2 device network port will cause the port to partition:

- a. An SQE signal active for more than 2048 bit times.

- b. A collision condition occurs during each of 32 consecutive attempts to transmit to that port.

Once a network port is partitioned, the IMR2 device will reconnect that port if the following is met:

- a. Standard reconnection algorithm—A data packet longer than 512-bit times (nominal) is transmitted or received by the partitioned port without a collision.

- b. Alternate reconnection algorithm—A data packet longer than 512-bit times (nominal) is transmitted by the partitioned port without a collision.

# **Basic Management Functions**

# **Repeater Management**

The IMR2 management functions are a super-set of the those provided by the AMD's IMR+/HIMIB device chipset. The IMR2 device contains the complete set of repeater and port functions as defined in ANSI/IEEE 802.3, *Repeater Management Standard*, (Section 19). All mandatory and optional capabilities are supported. These include the Basic Control, Performance Monitoring, and Address Tracking packages. Additionally, Node Address Mapping, MAU Management specific functions, and intrusion protection functions are included. Support is also provided for the RMON MIB RFC 1757.

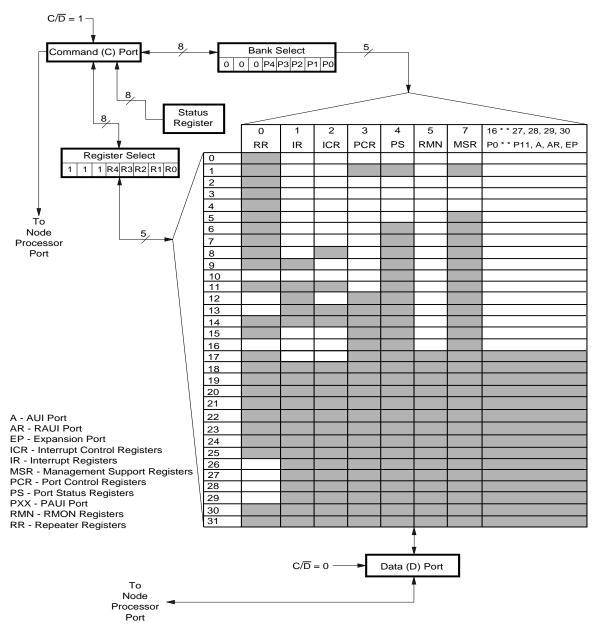

All information is stored in registers which can be accessed through the Microprocessor Interface (Node Processor Port). The register location is defined by a register bank and an address within that register bank. Address and data of the registers are multiplexed using the  $C/\overline{D}$  pin. The register address is selected by writing to the Node Processor Port with  $C/\overline{D}$  HIGH. The register data is selected by writing or reading to the Node Processor Port with  $C/\overline{D}$  LOW.

Many of the registers are larger than 1 byte. For these registers, consecutive accesses to register data (equal to the number of bytes in the register) are required. The order is LSByte to MSByte. For a write operation, if the address changes before all the bytes are written, the register is not changed to the new value.

The Status Register is accessed by reading the Node Processor Port with the  $C/\overline{D}$  pin HIGH. This reduces the number of operations necessary to access the Status Register.

All bit fields are ordered such that the left most bit is the most significant bit. Unused register banks, ports and register numbers are reserved and should not be accessed as this may cause device malfunction. When specifying the register bank or port number, the following format is used:

#### C Port Write

| 0   | 0 | 0 | P4 | P3 | P2 | P1 | P0  |

|-----|---|---|----|----|----|----|-----|

| MSB |   |   |    |    |    |    | LSB |

P4:0 represent the Register Bank or Port Number, organized as follows:

$$P = P_4 P_3 P_2 P_1 P_0$$

- P Port/Register Bank

- 0 Repeater Registers

- 1 Interrupt Registers

- 2 Interrupt Control Registers

- 3 Port Control Registers

- 4 Port Status Registers

- 5 RMON Registers

- 7 Packet Report Registers

- 16-30 Port Attributes

The register to be accessed for reading or writing is specified by writing the following control byte to the C register:

#### C Port Write

|   | 1   | 1 | 1 | R4 | R3 | R2 | R1 | R0  |

|---|-----|---|---|----|----|----|----|-----|

| ĺ | MSB |   |   |    |    |    |    | LSB |

$$R = R_4 R_3 R_2 R_1 R_0$$

Figure 1 shows the Management Register Map, and Table 1 shows register banks and register assignments within the register banks.

#### **RMON**

Remote monitoring (RMON) functions are designed to give the management system the capability to remotely monitor the hub for diagnostic purposes. The rules for RMON are described in the RMON MIB (as of this writing IETF RFC1578).

The IMR2 device provides direct support for both the statistics and history object groups. Indirect support is provided for the alarm, host, hostTopN, event, and matrix groups. Direct support is provided via the RMON register set and relevant attribute registers. Indirect support is provided through the Packet Report Port.

# **Packet Reports**

The IMR2 device generates status information on every packet that it repeats. The data is transmitted over the Packet Report Port. The data format consists of the beginning of the packet followed by a packet tag and statistical data on the packet.

| Preamble | DA | SA | T/L | Packet Data | Port No., | New |

|----------|----|----|-----|-------------|-----------|-----|

|          |    |    |     | Var. Length | Tag &     | FCS |

|          |    |    |     |             | Status    |     |

19879B-5

Figure 1. Management Register Map

Table 1. Management Registers

| Reg.<br>No. | Register Bank 0<br>Repeater Registers     | Register Bank 1<br>Interrupt Registers  | Register Bank 2<br>Interrupt Control<br>Registers | Register Bank 3 Port Control Registers           |

|-------------|-------------------------------------------|-----------------------------------------|---------------------------------------------------|--------------------------------------------------|

| 0           |                                           | Port Partition Status                   | Partition Change Interrupt                        | Alternative Partition                            |

|             |                                           | Change Interrupt                        | Enable                                            | Algorithm Enable                                 |

| 1           |                                           | Runts with Good FCS<br>Interrupt        | Runts with Good FCS Interrupt Enable              |                                                  |

| 2           |                                           | Link Status Change<br>Interrupt         | Link Status Change<br>Interrupt Enable            | Link Test Enable                                 |

| 3           |                                           | Loopback Error Change<br>Interrupt      | Loopback Error Change<br>Interrupt Enable         | Link Pulse Transmit<br>Enable                    |

| 4           |                                           | Polarity Change Interrupt               | Polarity Change Interrupt Enable                  | Automatic Receiver<br>Polarity Reversal Enable   |

| 5           |                                           | SQE Test Error Change<br>Interrupt      | SQE Test Error Change<br>Interrupt Enable         | SQE Mask Enable                                  |

| 6           |                                           | Source Address Changed<br>Interrupt     | Source Address Changed Interrupt Enable           | Port Enable/Disable                              |

| 7           |                                           | Intruder Interrupt                      | Intruder Interrupt Enable                         | Port Mobility Control                            |

| 8           |                                           | Source Address Match<br>Interrupt       |                                                   | Extended Distance<br>Enable                      |

| 9           |                                           |                                         | Multicast Address Pass<br>Enable                  | Last Source Address Automatic Intrusion Control  |

| 10          | Source Address Match<br>Register          | Data Rate Mismatch<br>Interrupt         | Data Rate Mismatch<br>Interrupt Enable            | Pref. Source Address Automatic Intrusion Control |

| 11          |                                           | ·                                       |                                                   | Last Source Address Lock<br>Enable               |

| 12          | Total Octets                              |                                         | Last Source Address<br>Compare Enable             |                                                  |

| 13          | Transmit Collisions                       |                                         |                                                   |                                                  |

| 14          |                                           |                                         |                                                   |                                                  |

| 15          |                                           | Transceiver Interface Status            | Preferred Address<br>Compare Enable               |                                                  |

| 16          | Configuration Register                    | Transceiver Interface Changed Interrupt | Transceiver Interface<br>Changed Interrupt Enable |                                                  |

| 17          |                                           | Jabber Interrupt                        | Jabber Interrupt Enable                           |                                                  |

| 18          |                                           |                                         |                                                   |                                                  |

| 19          |                                           |                                         |                                                   |                                                  |

| 20          |                                           |                                         |                                                   |                                                  |

| 21          |                                           |                                         |                                                   |                                                  |

| 22          |                                           |                                         |                                                   |                                                  |

| 23          |                                           |                                         |                                                   |                                                  |

| 24<br>25    |                                           |                                         |                                                   |                                                  |

| 26          | Panastar Status                           |                                         |                                                   |                                                  |

| 27          | Repeater Status  QuIET Device ID Register |                                         |                                                   |                                                  |

| 28          | Repeater Device and Revision Register     |                                         |                                                   |                                                  |

| 29          | Device Configuration                      |                                         |                                                   |                                                  |

| 30          |                                           |                                         |                                                   |                                                  |

| 31          |                                           |                                         |                                                   |                                                  |

**Table 1. Management Registers (Continued)**

| Reg. No. | _                            | Register Bank 5<br>RMON Registers | Register Bank 7<br>Management Support<br>Registers | Register Bank 16-30<br>Port Attribute Registers |

|----------|------------------------------|-----------------------------------|----------------------------------------------------|-------------------------------------------------|

| 0        | Partitioning Status of Ports | etherStatsOctets                  | Device ID                                          | Readable Frames                                 |

| 1        |                              | etherStatsPkts                    |                                                    | Readable Octets                                 |

| 2        | Link Test Status of Ports    | etherStatsBroadcastPkts           | Sample Error Status                                | Frame Check Sequence Errors                     |

| 3        | Loopback Error Status        | etherStatsMulticastPkts           | Report Packet Size                                 | Alignment Errors                                |

| 4        | Receive Polarity Status      | etherStatsCRCAlignErrors          | Statistics Control                                 | Frames Too Long                                 |

| 5        | SQE Test Status              | etherStatsUndersizePkts           |                                                    | Short Events                                    |

| 6        |                              | etherStatsOversizePkts            |                                                    | Runts                                           |

| 7        |                              | etherStatsFragments               |                                                    | Collisions                                      |

| 8        |                              | etherStatsJabbers                 |                                                    | Late Events                                     |

| 9        |                              | etherStatsCollisions              |                                                    | Very Long Events                                |

| 10       |                              | etherStats64Octets                |                                                    | Data Rate Mismatches                            |

| 11       |                              | etherStats65to127Octets           |                                                    | Auto Partition                                  |

| 12       |                              | etherStats128to255-               |                                                    | Source Address                                  |

| 12       |                              | Octets                            |                                                    | Changes                                         |

| 13       |                              | etherStats256to511-<br>Octets     |                                                    | Readable Broadcast<br>Frames                    |

| 14       |                              | etherStats512to1023-<br>Octets    |                                                    | Last Source Address                             |

| 15       |                              | etherStats1024to1518-<br>Octets   |                                                    | Readable Multicast Frames                       |

| 16       |                              | Activity                          |                                                    | Preferred Source<br>Address                     |

| 17       |                              |                                   |                                                    |                                                 |

| 18       |                              |                                   |                                                    |                                                 |

| 19       |                              |                                   |                                                    |                                                 |

| 20       |                              |                                   |                                                    |                                                 |

| 21       |                              |                                   |                                                    |                                                 |

| 22       |                              |                                   |                                                    |                                                 |

| 23       |                              |                                   |                                                    |                                                 |

| 24       |                              |                                   |                                                    |                                                 |

| 25       |                              |                                   |                                                    |                                                 |

| 26       |                              |                                   |                                                    |                                                 |

| 27       |                              |                                   |                                                    |                                                 |

| 28       |                              |                                   |                                                    |                                                 |

| 29       |                              |                                   |                                                    |                                                 |

| 30       |                              |                                   |                                                    |                                                 |

| 31       |                              |                                   |                                                    |                                                 |

#### **Detailed Functions**

This section describes the detailed functional behavior of the IMR2 device. Where necessary, the behavior is defined in terms of state machines. Note that this is a conceptual definition and the actual implementation may be different.

#### Reset

#### Hardware Reset

The IMR2 device enters the reset state when the  $\overline{RST}$  pin is driven LOW. The reset pin should be held LOW for a minimum of 150  $\mu s$  after power-up or 4  $\mu s$  otherwise. This allows the IMR2 device to reset the internal logic. During reset, the registers are set to their default values. The output signals are placed in their inactive state. That is, all analog outputs are placed in their idle state, all bidirectional signals are not driven, all active-HIGH signals are driven LOW, and all active-LOW signals are driven HIGH. The only exception is POL, which defaults to HIGH on reset. In a multiple IMR2 device repeater, the reset signal should be synchronized to MCLK when the expansion bus is operated in the synchronous mode.

Reset does not affect the RMON registers (Register Bank 5) or the Port Attribute Registers (Register Banks 16-30). These registers will power up at a random value. They can be preset while the IMR2 is in software reset or while the port is disabled via the microprocessor interface.

The mode of the expansion bus and the default state of the ports are set by XMODE and XENA during RST. XMODE sets the expansion bus mode and XENA sets the port state. Note that XENA only controls the default state. Once reset is completed, the enabling and disabling of the ports is under software control. The settings are as follow:

| XMODE   | 1 | The expansion bus is in the asynchronous (IMR2) mode.                                 |

|---------|---|---------------------------------------------------------------------------------------|

| XIVIODE | 0 | The expansion bus is in the synchronous (IMR/IMR+) mode.                              |

|         | 1 | All ports are enabled.                                                                |

| XENA    | 0 | All PAUI ports are disabled. The output drivers are placed in a high impedance state. |

#### Software Reset

The IMR2 device supports software reset with two bits on the Device Configuration Register: Repeater Reset (R - bit 7 on the register) and Management Reset (M - bit 6 on the register). Bit R resets the registers, repeater, and MAC engine. Setting Bit R is the functional equivalent of hardware reset, with the exception that the micro-

processor interface is not reset and the ability to access 4 and 6 byte attribute registers is maintained. Bit M affects only the management and intrusion protection functions of the IMR2 device.

Bit R causes the IMR2 device to go into the default state. As with hardware reset, all analog outputs are placed in their idle state, all bidirectional signals are not driven, all active-HIGH signals are driven LOW, and all active-LOW signals are driven HIGH. The only exception is POL, which defaults to HIGH on reset. Registers are also set to their default state.

Setting Bit R also allows write access to the MIB registers and some other read-only registers. These registers are the Total Octets Register, the Transmit Collision Register, the entire RMON Register Bank, and the Port Attribute Register Banks. Note that the Last Source Address Register and the Preferred Source Address Register can also be written into when bit R is not set. Setting bit R will not affect any bit of the Device Configuration Register. Thus, the IMR2 device does not automatically exit software reset. Software reset must be exited by setting bit R to zero.

The function of bit M is a subset of the function of bit R. It affects the intrusion protection and MIB registers. Setting bit M causes the intrusion protection registers to go into the default state. As with bit R, the MIB registers can be written into. 2 lists the default state of the registers. If the M column has an M, the corresponding register is set to its default state when bit M is set.

# **Expansion Bus**

The expansion bus has two modes of operation: the synchronous (IMR/IMR+ compatible) mode and the asynchronous mode. The modes are differentiated by the expansion bus clock. In the synchronous mode, the IMR2 devices (and any IMR/IMR+ devices) are all clocked by a single 20-MHz clock. The IMR2 device uses MCLK as the clock source.

In the asynchronous mode, IMR2 devices can be clocked (MCLK) by different sources. The single IMR2 device transmitting over the expansion bus provides the clock source for data. The clock pin in this mode is ECLK. ECLK clocks the data. All other expansion bus signals are asynchronous. The mode of expansion bus operation is selected during reset by XMODE.

The expansion bus can be configured for connection to a MAC. The pin  $\overline{\text{MACEN}}$  selects the MAC mode. When  $\overline{\text{MACEN}}$  is TRUE (LOW), the statistics on the data received by DAT are recorded in the management registers. The expansion bus is considered another port in the same sense as the PAUIs, the AUI, and the RAUI.

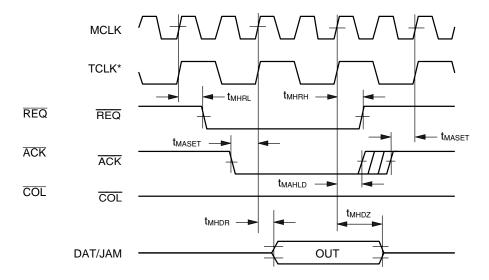

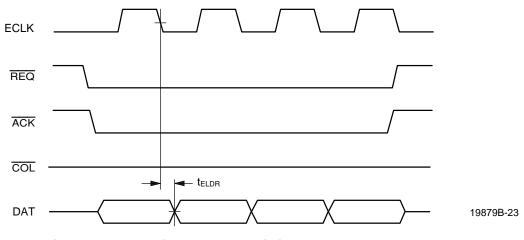

# Synchronous Mode Operation

While operating in the synchronous mode, the expansion bus pins are Data (DAT), JAM, Request ( $\overline{REQ}$ ), Acknowledge ( $\overline{ACK}$ ), and Collision ( $\overline{COL}$ ). DAT and JAM are bidirectional signals.  $\overline{REQ}$  is an output.  $\overline{ACK}$  and  $\overline{COL}$  are inputs.

Table 2. Register Reset Default States

| Register                               | Default   | М    |

|----------------------------------------|-----------|------|

| Configuration                          |           | M, R |

| Enable Interrupts                      | Masked    |      |

| Source Address Match                   | Masked    |      |

| Interrupt                              |           |      |

| Repeater Status                        |           |      |

| MJLP                                   | No Error  | R    |

| Device Configuration                   |           |      |

| Repeater Reset                         | Normal    |      |

| Management Reset                       | Normal    |      |

| RAUI Direction                         | Normal    |      |

| Loopback Test Mode                     | Normal    |      |

| Transceiver Loopback                   | Normal    |      |

| Partition Change Interrupt             | None      | R    |

| Runts with Good FCS Interrupt          | None      | M, R |

| Link Change Interrupt                  | None      | R    |

| Loopback Change Interrupt              | None      | R    |

| Polarity Changed Interrupt             | None      | R    |

| SQE Test No Change Interrupt           | None      | R    |

| Source Address Changed Interrupt       | None      | M, R |

| Intruder Interrupt                     | None      | M, R |

| Source Address Match Interrupt         | None      | M, R |

| Data Rate Mismatch Interrupt           | No        | R    |

|                                        | Mismatch  |      |

| Transceiver Interface Status           | No Trans. | R    |

| Transceiver Interface Change Interrupt | None      | R    |

| Jabber Interrupt                       | No Jabber | R    |

| Partition Change Interrupt Enable      | Masked    | R    |

| Runts with Good FCS Interrupt Enable   | Masked    | M,R  |

| Link Changed Interrupt Enable          | Masked    | R    |

| Loopback Changed Interrupt Enable      | Masked    | R    |

| Polarity Changed Interrupts Enable     | Masked    | R    |

| SQE Test Changed Interrupt Enable      | Masked    | R    |

| Register                                       | Default   | М    |

|------------------------------------------------|-----------|------|

| Source Address Changed Interrupt Enable        | Masked    | M,R  |

| Intruder Interrupt Enable                      | Masked    | M, R |

| Multicast Address Pass Enable                  | Disabled  | M, R |

| Data Rate Mismatch Interrupt<br>Enable         | Masked    | R    |

| Source Address Compare Enable                  | Disabled  | M, R |

| Preferred Address Compare Enable               | Disabled  | M, R |

| Transceiver Interface Changed Interrupt Enable | Masked    | R    |

| Jabber Interrupt Enable                        | Masked    | R    |

| Alternative Partition                          | Disabled  | R    |

| Link Test Enable                               | Enabled   | R    |

| Link Pulse Enable                              | Enabled   | R    |

| Reverse Polarity Enable                        | Disabled  | R    |

| SQE Mask Enable                                | Disabled  | R    |

| Port Enable                                    | Enabled   | R    |

| Port Mobility Control                          | XENA      | R    |

| Extended Distance Control Enable               | Disabled  | R    |

| Source Address Automatic Intrusion Enable      | Disabled  | R    |

| Preferred Address Automatic Intrusion Enable   | Disabled  | R    |

| Last Source Address Lock Enable                | Disabled  | M, R |

| Partition Status                               | Connect   | R    |

| Link Status                                    | Link Fail | R    |

| Loopback Status                                | No Error  | R    |

| Polarity Status                                | Positive  | R    |

| SQE Test Status                                | No Error  | R    |

| Sample Counter Que                             | Four      | M, R |

| Packet Report Packet Size                      | 07FF'     | M, R |

| Statistics Control                             |           |      |

| Stat Tag                                       | Disable   | M, R |

| FCS Tag                                        | Disable   | M, R |

The IMR2 device expansion scheme allows the use of multiple IMR2 devices in a single-board repeater or in a modular multiport repeater with a backplane architecture. Data sent on the DAT line is in NRZ format and is synchronized to MCLK. Another bidirectional pin, JAM, is used to communicate internal IMR2 device status from the single active IMR2 device to other IMR2 devices in the system. This signal indicates whether the active IMR2 device is in a collision state.

Arbitration for control of the bussed signals, DAT and JAM, is provided by external circuitry. One output pin  $(\overline{\text{REQ}})$  and two input pins  $(\overline{\text{ACK}}$  and  $\overline{\text{COL}})$  are used as arbitration signals. The IMR2 device asserts  $\overline{\text{REQ}}$  to

indicate that it is active and is ready to drive the DAT and JAM signals. The external arbiter asserts  $\overline{ACK}$  if one and only one IMR2 device has  $\overline{REQ}$  asserted. This allows the corresponding IMR2 device to drive the DAT line with data to be repeated by all other IMR2 devices. If there is more than one IMR2 device asserting  $\overline{REQ}$ , the external arbiter should assert  $\overline{COL}$ , indicating multiple IMR2 devices are active.

The active IMR2 device drives the JAM line HIGH in order to signal other IMR2 devices that it has detected a collision across one or more of its ports and is generating a Jam Sequence. The DAT line is used during single IMR2 device collision (JAM asserted) to signal single-port collision (DAT HIGH) or multiport collision (DAT LOW). Other IMR2 devices synchronize their internal Collision Jam Sequence generators using JAM and DAT pins as inputs.

If more than one IMR2 device is active (multiple REQs asserted), the external arbiter should assert the COL line to signal this condition. In this case, all IMR2 devices in the repeater are forced into the multiport collision state and will generate Jam sequence independently while this condition lasts. As ports on separate IMR2 devices back off, the last IMR2 device with an active port regains control of the DAT and JAM signals and all other IMR2 devices will continue generating Jam sequence while the JAM signal is asserted.

In a typical single-board application, three IMR2 devices can be connected together without the use of external transceivers. The total number of IMR2 devices that can be used in a more complex architecture will depend on the drive capability, system timing limitations, and system design.

The external arbiter is required to generate two signals  $(\overline{ACK} \text{ and } \overline{COL})$ . The logic function for these signals in a three IMR2 device Repeater Unit is as follows:

ACK = REQ1 & !REQ2 & !REQ3 + !REQ1 & REQ2 & !REQ3 + !REQ1 & !REQ2 & REQ3

COL = !(ACK + !REQ1 & !REQ2 & !REQ3)

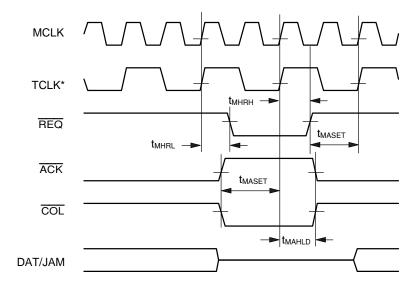

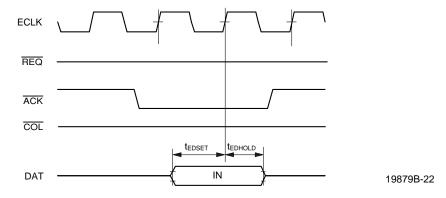

#### Asynchronous Mode Operation

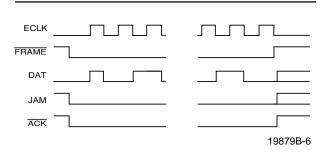

The operation of the expansion bus in the asynchronous mode is similar to the operation in the synchronous mode. The primary difference is that the clock signal in the asynchronous mode is ECLK, which is sourced by the IMR2 device transmitting DAT. The signals JAM,  $\overline{\text{REQ}}$ ,  $\overline{\text{ACK}}$ , and  $\overline{\text{COL}}$  are all asynchronous.

DAT is synchronized to ECLK, which is a 10-MHz clock signal. When the IMR2 device asserts  $\overline{\text{REQ}}$  and receives an  $\overline{\text{ACK}}$ , ECLK is an output. When the IMR2 device does not assert  $\overline{\text{REQ}}$  and receives an  $\overline{\text{ACK}}$ , ECLK is an input.

In the asynchronous mode, it is probable that ECLK and the master clocks of the receiving IMR2 devices will be

skewed in frequency. To help the IMR2 devices accommodate the frequency differences, the expansion bus transmits a framing signal (FRAME). See Figure 2.

Because JAM is an asynchronous signal, there is no defined relationship between JAM and ECLK.

Figure 2. Asynchronous Mode Data Transfer

#### **Packet Statistics**

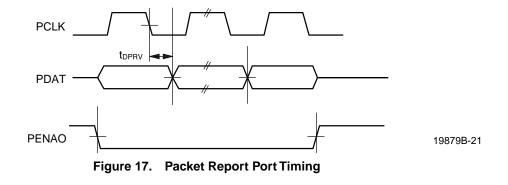

# Packet Report Port

For each packet, the IMR2 device can compile a set of data about that packet. This data, which will now be referred to as the report packet, allows the system to derive objects in the Host, HostTopN, and Matrix groups of the RMON MIB (RFC 1757). The Report Packet is delivered by the Packet Report Port (PR).

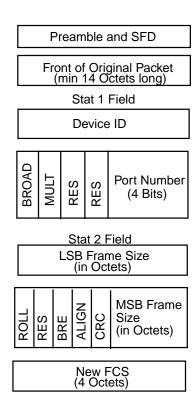

The PR port transmits a portion of the packet along with data about that packet to a MAC. The format of the report packet is shown in 3. Sending only a portion of the packet is referred to as packet compression.

The degree to which the original packet is compressed is set by the Report Packet Size Register. The size is in bytes. If the register is set to 14 or less, the size of the packet passed is 14 bytes. If the register is set to 1536 or greater, the entire packet is passed. If the packet size is equal to or less than the value set in the Report Packet Size Register, the entire packet is passed.

If the destination address of the packet is the same as the address of the MAC connected to the PR Port, then it is desirable to have the entire packet transmitted to the MAC. Therefore, packet compression is automatically disabled when the destination address of the packet is a valid address for the expansion bus. However, the report tag is appended to the end of the packet. Note that the entire packet is also sent if the destination address is a broadcast address.

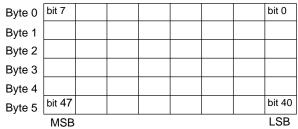

BROAD - Broadcast Address Match MULT - Multicast Address Match RES - Reserved. Set to Zero. ROLL- Frame Size has exceeded 1535 bytes BRE - Bit Rate Error

BRE - Bit Rate Error

ALIGN - Framing Error

CRC - CRC Error

**Note**: The bit designation is LSB to the left and MSB to the right. The fields are transmitted LSB first.

19879B-7

#### Figure 3. Detailed Report Packet

The presence of a valid destination address is determined by comparing the destination address of the packet with the Last Source Address Register and the Preferred Source Address Register associated with the expansion bus. Comparison is enabled by setting the EP bit of the Last Source Address Compare Enable Register and/or the Preferred Source Address Compare Enable Register. Setting the EP bit of the Multicast Address Pass Enable Register inhibits compression when the address is a multicast address.

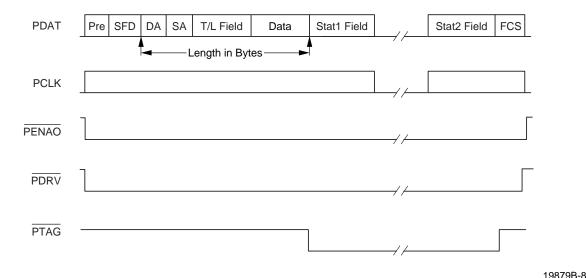

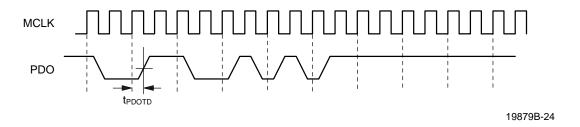

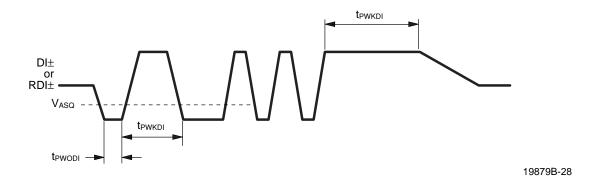

The PR port has six signals: PCLK, PDAT, PENAO, PENAI, PDRV, and PTAG. PCLK is a 10-MHz clock signal. PDAT transmits the packet data and is clocked by the rising edge of PCLK. PENAO is an active-LOW signal and indicates when the PR port is active. PENAI senses when a PR port of another IMR2 device is active and is an active-LOW signal. PDRV is used to enable an external buffer for PCLK and PDAT. PTAG indicates when the tag is being transmitted.

The signal format is shown in 4. PDAT first transmits the compressed or uncompressed packet. Then it transmits the first status field. This field has the format of the first statistics field shown in 4. At the end of the first statistics field, PCLK is stopped until the end of the packet. Then the second statistics field is transmitted over PDAT along with a new FCS.

Multiple IMR2 devices can be connected to a single MAC. If an IMR2 device becomes active while another device is transmitting statistics, the new packet will not be transmitted over the PR port.

#### RAUI Port

The RAUI Port is a configurable AUI port. It has the same signals that are associated with an AUI port: DO, DI, and CI. For the RAUI Port, these are named RDO, RDI, and RCI, respectively. The RAUI port can be configured in either normal or reverse mode. When configured in normal mode (default mode), the functionality is that of an AUI port on a MAC. When configured in reverse mode, the RAUI port provides the functionality of an AUI port on a MAU, with RCI acting as an output. This reverse configuration allows the RAUI Port to be connected directly to a MAC. However, the sense of RDO and RDI does not change with the configuration. Therefore, in the reverse configuration RDO should be connected to DI of the MAC and RDI should be connected to DO on the MAC.

Table 3. RAUI Port

| Device Configuration<br>Register Bit 5 | RAUI Port Mode                     |

|----------------------------------------|------------------------------------|

| 0                                      | Normal Mode                        |

| 1                                      | Reverse Mode<br>(RCI is an Output) |

Figure 4. Packet Port Signals

#### **Error Packet Statistics**